Pipelining, Processing, and Multi-Threading Explained

Let's start by talking about processor datapaths and instruction types.

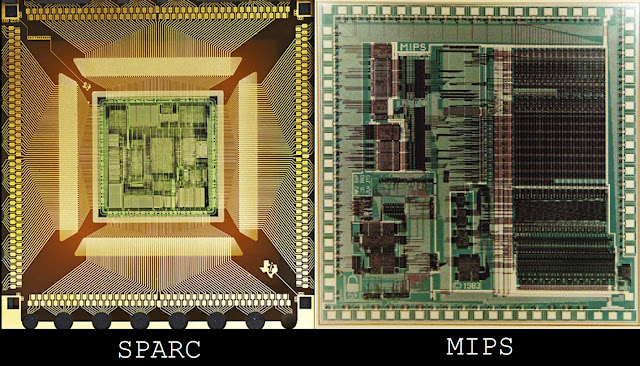

The datapath defines how processors perform operations and handle data movement. When comparing the MIPS (Microprocessor without Interlocked Pipeline Stages) and SPARC (Scalable Processor Architecture) processors, there are core differences in hardware, architecture and design that effect performance, power consumption, and processing capability. These differences are defined in the datapath.

In both processors, the datapath is composed of several components including the ALUs, registers, multiplexers, and memory units. As instructions are executed, there are different ways of performing instructions depending on the type of instruction and where the data is located.

There are 5 types of instructions:

- R-Type: Used for register-based arithmetic, logical operations, and shifts.

- I-Type: Used for immediate arithmetic, memory access, and branch operations.

- J-Type: Used for jump operations.

- Special Instructions: Used for operations like no-op and system calls.

- Floating-Point Instructions: Used for floating-point arithmetic, typically handled by a coprocessor.

The most common assembly language instructions are the R-type instructions and the Memory instructions. So, how do the datapaths for R-type and Memory instructions differ?

Basically, R-Type are basic operations that access the operands from registers. Memory instructions need to access memory to access the operand and load it into registers to them perform the instruction.

- R-Type instructions typically handle arithmetic, logical operations, and some special functions, specifically add, sub, shift left, AND, OR and Set On Less Than. These instructions operate solely on registers and do not access memory.

- Memory instructions are a subset of I-Type instructions that transfer data to and from memory using the load and store instructions. These memory instructions work by using a series of machine instruction steps in lw (load word) and sw (store word) instruction datapaths.

The R-Type instructions typically require fewer clock cycles because the data is already loaded into the registers and the MEM datapath step does not use any cycles to compute the memory address and access memory.

Memory instructions typically have latency due to added clock cycles needed to compute the effective memory address and access the data element at that address.

MIPS and SPARC datapaths are different.

MIPS processor datapath is designed without pipelining. In this design, instructions are processed one-by-one from an instruction queue. The SPARC processor has pipelining baked into the processor to optimize the clock cycles needed to complete computations. Pipelining enables multi-threading capabilities in the SPARC processor.

MIPS datapath:

- Fetch (IF)->Decode (ID)->Execute (EX)->Memory Access (MEM), and Write Back (WB)

Multi-Threading

The Sparc core pipeline is similar to the MIPS core pipeline containing the same machine instruction steps but contains a thread management step. Thread management occurs in the Thread Selection (ThrdSel) that is performed after the Fetch step where a thread is selected to execute in the next processor cycle.

SPARC datapath:

- Fetch (IF)->Thread Select (ThrdSel)->Decode (ID)->Execute (EX)->Memory Access (MEM), and Write Back (WB)

Thread selection supports multi-threading and was designed for enhanced efficiency. Multi-threading basically means the processor can run multiple process threads in parallel by using context switching, thread scheduling and resource sharing.

Multi-threading can also load the next instruction in unused data space in a cycle, run the next instruction while another thread is awaiting data or resources, and prioritizing processes to run first.

Summary

Understanding how instructions are carried out in the processor is key to developing optimized hardware, firmware and software. Processors can be designed in different ways depending on the system requirements and how the computer will be used.

Comments

Post a Comment